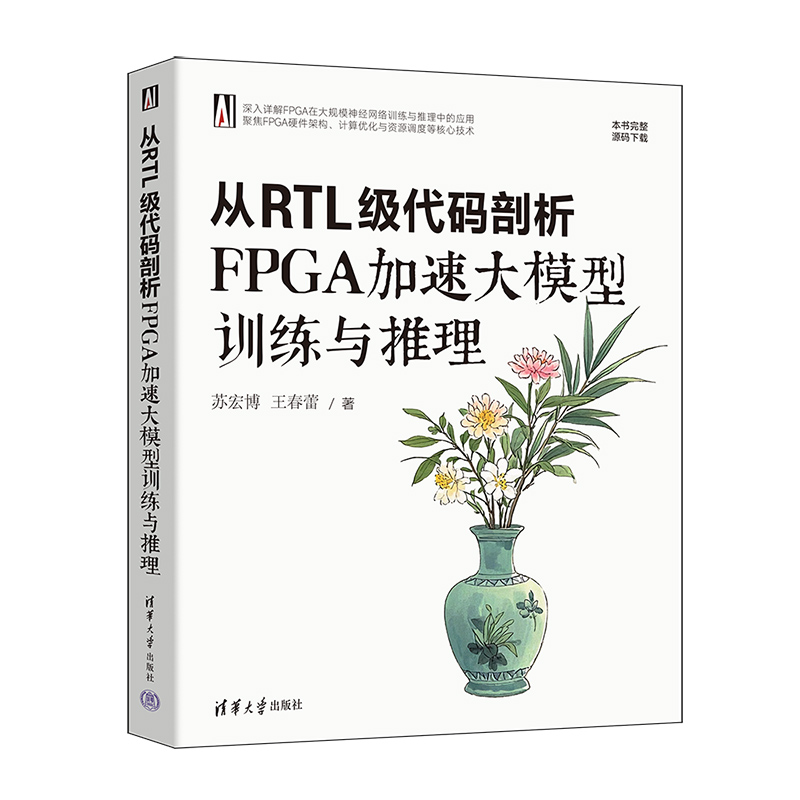

作者:苏宏博、王春蕾

定价:129元

印次:1-1

ISBN:9787302704829

出版日期:2026.01.01

印刷日期:2025.12.12

图书责编:王金柱

图书分类:零售

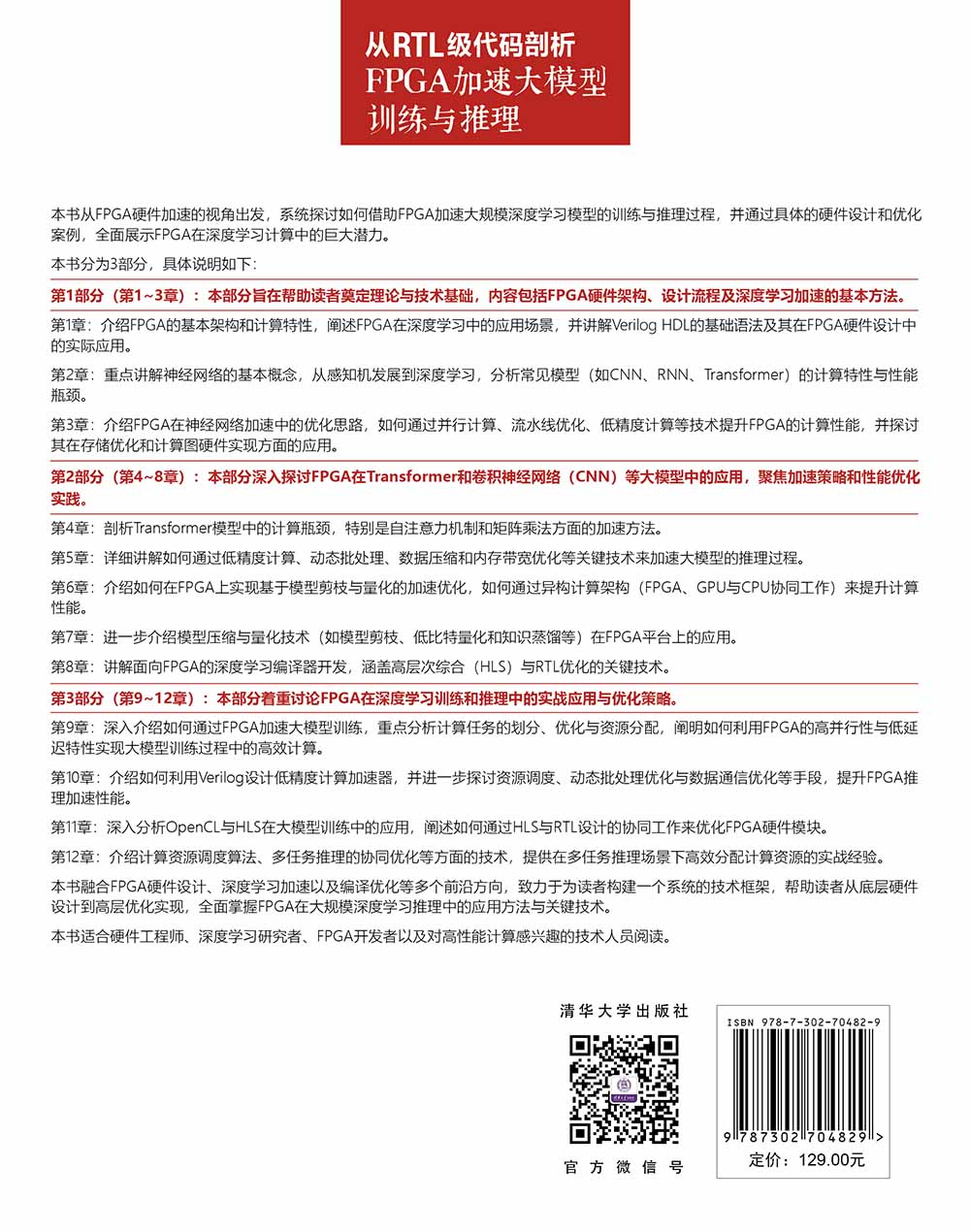

"《从RTL级代码剖析FPGA加速大模型训练与推理》系统而深入地介绍了FPGA在大规模神经网络训练与推理中的应用,重点聚焦于FPGA的硬件架构、计算优化与资源调度等技术。《从RTL级代码剖析FPGA加速大模型训练与推理》共分为12章,内容涵盖FPGA与Verilog HDL基础、FPGA的基本架构、深度学习算法的计算特性、硬件加速的基本思路、模型压缩与量化技术、FPGA在Transformer模型中的应用、大模型训练的硬件优化、异构计算架构中的FPGA角色,以及面向FPGA的深度学习编译器开发。《从RTL级代码剖析FPGA加速大模型训练与推理》对FPGA硬件设计、计算资源调度、硬件优化等技术进行了详尽分析,读者可以从中获得利用FPGA加速深度学习计算的核心方法与思路。 通过理论与实践相结合,《从RTL级代码剖析FPGA加速大模型训练与推理》为读者提供了一套从硬件设计到算法优化的完整知识体系。无论是希望深入学习FPGA设计的学生,还是正在从事FPGA加速开发的专业工程师,都能从本书中获得丰富的专业知识与实用的工程技能。"

"苏宏博,毕业于哈尔滨工业大学,博士,长期AI相关工程及研究,致力于解决数学建模、数据分析、机器学习等工程、大模型应用问题,在国内外期刊发表学术论文十余篇,授权专利多项。王春蕾,毕业于四川大学,研究生学历,先后就职于中车集团和中国核动力研究设计院。长期从事电力电子与电力传动、通信工程、自动控制等领域的科研及工程设计工作,参与多项重大项目的FPGA软件设计和开发工作,拥有十年以上FPGA架构设计与RTL级代码开发经验。"

前 言 随着深度学习的迅猛发展,大规模神经网络已广泛应用于自然语言处理、计算机视觉和语音识别等领域,并逐步渗透到各行各业。大模型对计算资源的需求不断攀升,特别是在训练和推理阶段,计算任务的复杂度和规模已远超传统处理器的处理能力。 为应对这一挑战,硬件加速技术应运而生,尤其是FPGA(Field Programmable Gate Array,现场可编程门阵列),凭借其高度的并行计算能力和设计灵活性,成为深度学习加速中的重要解决方案。 本书从FPGA硬件加速的视角出发,系统探讨如何借助FPGA加速大规模深度学习模型的训练与推理过程,并通过具体的硬件设计和优化案例,全面展示FPGA在深度学习计算中的巨大潜力。 本书分为3部分,循序渐进地引导读者从理论基础迈向实战应用,全面掌握FPGA加速深度学习的核心技术。 第1部分:FPGA与深度学习基础。本部分旨在帮助读者奠定坚实的理论与技术基础,内容包括FPGA硬件架构、设计流程及深度学习加速的基本方法。 ?第1章:介绍FPGA的基本架构和计算特性,阐述FPGA在深度学习中的应用场景,并讲解Verilog HDL的基础语法及其在FPGA硬件设计中的实际应用。 ?第2章:重点讲解神经网络的基本概念,从感知机发展到深度学习,分析常见模型(如CNN、RNN、Transformer)的计算特性与性能瓶颈。 ?第3章:聚焦FPGA在神经网络加速中的优化思路,介绍如何通过并行计算、流水线优化、低精度计算等技术提升FPGA的计算性能,并探讨其在存储优化和计算图硬件实现方面的应用。 第2部分:FPGA在大模型加速中的应用。本部分深入探...

第 1 部分 FPGA与深度学习基础

第 1 章 FPGA与Verilog HDL基础 2

1.1 FPGA的基本架构与计算特性 2

1.1.1 FPGA的基本架构:LUT、BRAM、DSP与互连 2

1.1.2 FPGA的并行计算特性及其相较于GPU、CPU的优势 4

1.1.3 FPGA在深度学习中的主要应用场景 6

1.2 Verilog HDL基础:从硬件描述到综合 7

1.2.1 Verilog HDL的基本语法与结构 8

1.2.2 组合逻辑、时序逻辑与有限状态机(FSM)设计 18

1.2.3 FPGA综合优化:面积、速度与功耗的权衡 21

1.3 FPGA设计流程与EDA工具链 23

1.3.1 从RTL到Bitstream:FPGA的基本设计流程 24

1.3.2 Vivado、Quartus与Synplify:主流EDA工具解析 26

1.3.3 FPGA硬件仿真、调试与后端实现 29

1.4 FPGA存储架构与数据优化 31

1.4.1 FPGA内存体系:BRAM、SRAM、DDR与HBM 32

1.4.2 数据搬移优化:DMA、AXI总线与片上缓存策略 33

1.4.3 计算资源优化:流水线、并行计算与算子融合 34

1.5 FPGA、ASIC与GPU:AI计算加速方案对比 35

1.5.1 GPU加速大模型计算的特点与限制 35

1.5.2 ASIC在AI计算中的优势 36

1.5.3 FPGA的灵活性与计算优化能力对比 36

1.6 本章小结 3... 查看详情

"在大模型算力需求呈指数级增长的当下,FPGA 以其可编程性与高能效比,成为突破深度学习训练与推理瓶颈的关键硬件方案。《从RTL级代码剖析FPGA加速大模型训练与推理》堪称 FPGA加速大模型领域的 “全景式指南”,既立足理论根基,又深耕实战落地,为不同背景的读者搭建起从入门到精通的完整学习路径。

全书以 “基础 — 应用 — 实战” 的逻辑层层递进:第一部分系统梳理 FPGA 硬件架构、Verilog 编程基础与深度学习模型计算特性,破解 “硬件与算法如何适配” 的核心疑问;第二部分直击大模型加速痛点,针对 Transformer、CNN 等主流模型,深入剖析并行计算、低精度量化、模型压缩等关键优化技术,更涵盖异构计算、编译器开发等前沿方向;第三部分通过训练任务优化、推理性能调优、多任务资源调度等实战案例,将 RTL 设计、HLS 开发等技术落地为可复用的工程经验。

《从RTL级代码剖析FPGA加速大模型训练与推理》以清晰的结构、详实的案例、深度的技术剖析,填补了 FPGA 硬件设计与深度学习部署之间的知识鸿沟,是解锁大模型高效算力的必备工具书。无论是希望深入学习FPGA设计的学生、硬件工程师、专注算法创新的深度学习开发者,还是探索高性能计算的技术爱好者,都能从书中获得精准赋能。"

电子书

电子书

在线购买

在线购买

分享

分享